**ASICs**

# Semicustom QuickChip ASICs Implement RF Functions to 9GHz

Maxim has two different approaches for developing HF ASICs: a semicustom QuickChip design methodology and the more traditional full-custom design methodology. The semicustom design approach is discussed below and provides a low-cost, fast turn-time approach for developing customerdesigned RF ASICs.

In addition to standard product ICs, Maxim offers a rapid-response ASIC service. Semicustom arrays known as "QuickChips™ provide designers with a selection of uncommitted semiconductor devices: JFETs, Schottky diodes, ESD-protected diodes, MOS capacitors, trimmable nichrome resistors, and bipolar transistors with fTs to 27GHz. Completing one of these chips with a custom metal mask set interconnects the selected components to create a high-frequency, high-performance circuit.

A comprehensive set of design, verification, and layout software tools has been developed to ensure a high probability that QuickChip designs will meet their target specifications on the first pass. Both UNIX and PC platforms are supported.

Three different QuickChip families are available. The QC10 family of seven arrays is made with a complementary bipolar process featuring NPN and PNP fTs of 9GHz and 6GHz, respectively. It is optimized for analog signal acquisition, amplification, and sourcing.

The QC6 family of four arrays is fabricated in a process with 9GHz NPN and 80MHz PNP fTs. These arrays are suitable for a wide range of fiber, IF, and instrumentation applications.

The QC9 array is fabricated in a 27GHz process and is intended for RF and HF applications. More than 35 designs have been completed using the QC9 array since its introduction. These include a 900MHz transceiver, a 7GHz prescaler, several GPS receivers, an OC48 amp-lifier, pulse and window comparators, and a 2x2 crosspoint switch.

The design examples that follow, reprinted with kind permission of the IEEE, illustrate the capabilities of QuickChip ASICs.

For further information, or to request a copy of Maxim's High-Frequency ASIC Development

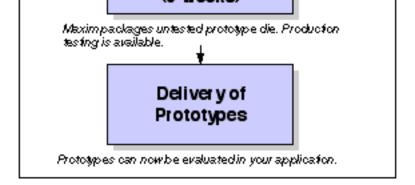

#### Maxim's Quick Chip IC Design Approach

#### ASIC Definition

Determine feasibility, establish initial objective specification, select process, select Quick Chip and package option, order software. Sample device simulation models are available to aid process selection.

### Software Training (2 days)

Maxim engineers train you to use the Guick Chip Design Tools included in the Guick Tools package: Analog Design System (schematic capture and simulator), GuERC (electrical rule checker), and Guic Ric (layout editor).

## Design & Layout (project dependent)

Design and simulate the circuit check for electrical rule violations with QuEAC, and lay out your circuit design using QuicKic. Maxim reviews both the circuit design and layout

#### Tapeout (2 weeks)

Maximperforms the final layout versus schematic verification, electrical rule check, and layout design rule check before tapeout. Upon successful completion of final design database verification and a signed customer layout release, Maxim orders masks.

> Wafer Fabrication (4 weeks, QC6/QC10) (6 weeks, QC9-60D)

Maxim fabricates die using 3 to 6 QuickChip nichrome, metal, and via masks.

> Die Prep & Packaging (3 weeks)

Maxim packages untested prototype die. Production testing is available.

QuickChip is a trademark of Maxim Integrated Products.